## A Novel Charge Pump PLL with Reduced Jitter Characteristics

Myoung-Su Lee, Tae-Sik Cheung, and Woo-Young Choi Dept. of Electronic Engineering, Yonsei University, 134, Shinchon-dong, Seodaemun-ku, Seoul, 120-749, Korea. phone : +82-2-361-2874

fax : +82-2-312-4584

e-mail : lms@semicon4.yonsei.ac.kr

## Abstract

A new charge pump structure is proposed that can improve jitter characteristics of a Phase-Locked Loop (PLL) by blocking the control voltage leakages. The new structure also has low power consumption because it uses a self-biased method that switches the current flow only on demand. A PLL with the proposed charge pump is designed with  $0.6\mu$ m CMOS process technology and evaluated by post-layout simulation. frequency divider's output signal V<sub>div</sub>, and produces UP and DN signals that, through the charge pump and the loop filter, control Voltage Controlled Oscillator (VCO), When PLL is locked, two outputs of PFD should be the same and the charge pump output should be constant. In practice, however, this does not happen as the charge pump circuit usually has asymmetric features that cause VCO control voltage changes and PLL output frequency noises. А new charge pump structure is proposed that minimizes this problem.

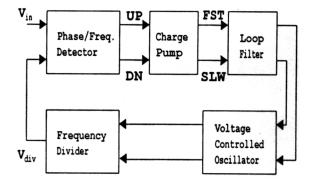

Fig 1. Block diagram of PLL

PLL optimization for high frequency operation has been studied by many researchers(1-3). The PLL structure can be divided into five parts as shown in Fig 1. The phase/frequency detector (PFD) detects the phase difference between external input signal V<sub>in</sub> and

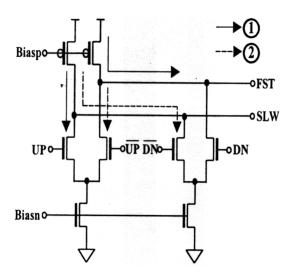

Fig 2. Conventional charge pump

Figure 2 shows a conventional structure for

0-7803-5727-2/99/\$10.00 © 1999 IEEE - 596 -

the charge pump. When UP signal is logic '1' and DN signal logic '0', FST node is charged ∼ SLW node is discharged. When PLL is 1 lucked. UP and DN signals are both logic '0'. except during PFD's reset time in which case they are logic '1'. When UP and DN are logic '0', current path 2 is established, and when '1', current path ① is they are logic established. Consequently, even when PLL is locked, path ① and ②consume power. In this case, the current driving ability of PMOS is lower than NMOS if the control voltage is higher than the bias voltage (1.65V). Such changes in the control voltages cause noises in VCO output. As the difference between the charge pump's output voltages and the bias change voltage increases. the voltage increases.

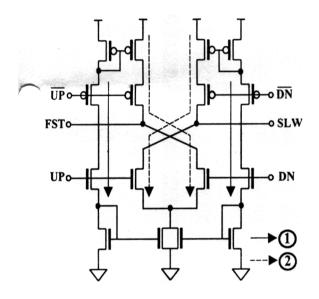

Fig 3. Proposed charge pump

new charge \_ pump structure that Α minimizes such a problem is shown in Fig 3. The suggested charge pump uses а method and functions self-biased as а charge pump. It has current differential mirrors which establish current path 2 from path ①. When PLL is locked, UP and DN gnals are logic '0', and PMOS and NMOS are both turned off. The control voltage is constant because FST and SLW node's current paths are blocked. As a result the PLL output noise is reduced.

Two PLL circuits including structures shown in Fig. 2 and Fig. 3 are designed with  $0.6 \mu m$  CMOS process parameters.

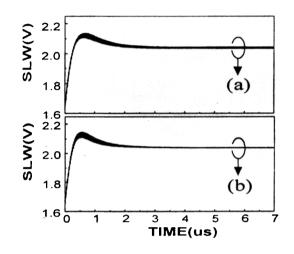

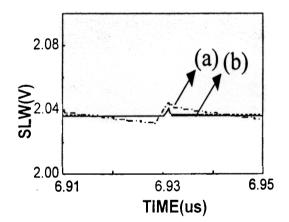

Fig 4. The control voltage of the PLL (a) Conventional (b) Proposed

Fig 5. Magnification of Fig 4.

Conventional configurations are used for PFD and VCO. The VCO center frequency is 650MHz. The simulation results for 28ns input period is shown in Fig. 4 and 5. Figure 4 (a) and (b) are SLW node voltages for a PLL with conventional and proposed charge pump structures, respectively. As can be seen, the proposed charge pump has much reduced SLW node voltage changes. Figure 5 shows the magnified waveforms.

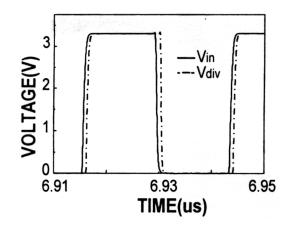

Fig 6. Input/output waveforms of conventional charge pump PLL

Fig 7. Input/output waveforms of proposed charge pump PLL

Figure 6 shows Input/output waveforms of conventional charge pump PLL with 28ns input period and Figure 7 shows that of proposed charge pump PLL. Comparing Fig. 6 with Fig. 7, proposed charge pump also reduces phase offset of PLL.

## Conclusion

A new charge pump PLL was proposed and designed. The design was done with  $0.6\mu$ m CMOS process parameters for +3.3V power supply. Post-layout simulation shows that the proposed circuit has reduced leakage currents for VCO control voltages and, consequently the VCO output frequency is more stable.

## Reference

- J. G. Maneatis, "Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques," IEEE J. Solid-State Circuits, vol. 31, no. 11, pp. 1723-1732, 1996.

- (2) S. O Jeon, T. S. Cheung, and W. Y. Choi, "Phase/frequency detectors for high-speed PLL applications," IEE Electronics Letters, vol. 34 no 22, pp. 2120-2121, publication, 1998.

- (3) Sungjoon Kim, et al., "A 960-Mb/s/pin Interface for Skew-Tolerant Bus Using Low Jitter PLL," IEEE J. Solid-State Circuits, vol. 32, no. 5, pp. 691-700, 1997.