No.: 1142181

### PATENT CERTIFICATE FOR INVENTION

Woo-Young CHOI ; Pyung-Su HAN

ZL 200810188109.7

TITLE OF INVENTION:

BIT-TRANSITION POINT EXTRACTION CIRCUIT AND PHASE-LOCKED CLOCK RECOVERY CIRCUIT FOR NRZ-RECOVERY SIGNAL AND METHOD FOR CONTROLLING THE CIRCUIT

INVENTOR:

PATENT NO.:

FILING DATE OF APPLICATION: December 12, 2008

PROPRIETOR OF PATENT RIGHT:

INDUSTRY-ACADEMIC COOPERATION FOUNDATION, YONSEI UNIVERSITY

PUBLISHED DATE OF APPLICATION: February 27, 2013

After the examination was performed according to the Patent Law, the present Office decides hereby to issue a patent right and the present Patent Certificate, and to register the right on the Patent Record. The Patent Right will be effective as of the date of announcement of granting the Patent Right.

The term of the present patent is twenty years, counting from the filing date. Proprietor of Patent Right should pay annuities according to the provisions prescribed in the Patent law and the Implementing Regulation. Payment of annuities for the present patent shall be exercised within one month prior to December 12, each natural year. Failure to pay a prescribed annuity would result in the patent right ceasing when the term for payment of said annuity expires.

The present Certificate discloses items of the legal status as same as the patent right was recorded. Items of assignment, succession, cancellation, invalidation, and cessation of patent right, as well as change of Proprietor's name, nationality, address, etc., are recorded on the Patent Record.

Director General TIAN Lipu

Date: February 27, 2013

证书号第1142181号

发明专利证书

发 明 名 称: 非归零恢复信号的比特转换点提取电路和锁相时钟恢复电路以及用于控制所述电路的方法

发 明 人: 崔佑荣;韩平洙

专利号: ZL 2008 1 0188109.7

专利申请日: 2008年12月12日

专 利 权 人: 延世大学工业学术合作社

授权公告日:2013年02月27日

本发明经过本局依照中华人民共和国专利法进行审查,决定授予专利权,颁发本证书 并在专利登记簿上予以登记。专利权自授权公告之日起生效。

本专利的专利权期限为二十年,自申请日起算。专利权人应当依照专利法及其实施细则规定缴纳年费。本专利的年费应当在每年12月12日前缴纳。未按照规定缴纳年费的, 专利权自应当缴纳年费期满之日起终止。

专利证书记载专利权登记时的法律状况。专利权的转移、质押、无效、终止、恢复和专利权人的姓名或名称、国籍、地址变更等事项记载在专利登记簿上。

## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 101753130 B (45) 授权公告日 2013. 02. 27

- (21)申请号 200810188109.7

- (22)申请日 2008.12.12

- (73) 专利权人 延世大学工业学术合作社 地址 韩国首尔

- (72)发明人 崔佑荣 韩平洙

- (74) 专利代理机构 北京康信知识产权代理有限 责任公司 11240

代理人 余刚 尚志峰

(51) Int. CI.

*H03K 19/0948* (2006.01)

*H03L 7/08*(2006.01)

(56)对比文件

US 3947637, 1976.03.30,

- CN 1328383 A, 2001. 12. 26,

- US 2006055472 A1, 2006. 03. 16,

- US 6249192 B1, 2001. 06. 19,

审查员 姜晓庆

#### (54) 发明名称

非归零恢复信号的比特转换点提取电路和锁 相时钟恢复电路以及用于控制所述电路的方法

#### (57) 摘要

本发明提供了一种比特转换点提取电路装置,包括:预定的电流源晶体管;与源极连接的晶体管对,所述源极向电流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号;以及电容器,与晶体管对和电流源晶体管连接,以使电流源晶体管的输出节点的电压恒定。

权利要求书 2 页 说明书 8 页 附图 13 页

CN 101753130 B

1. 一种使用比特转换点提取电路的时钟恢复电路装置,包括:

预定的电流源晶体管;

晶体管对,其源极连接在一起,所述源极向所述电流源晶体管偏置,并且所述晶体管对 通过其栅极被施加有来自外部的差分非归零恢复输入信号;

电容器,与所述晶体管对和所述电流源晶体管连接,以使所述电流源晶体管的输出节 点的电压恒定;以及

LC 电压控制振荡器,所述 LC 电压控制振荡器向预定的差分输出端输入由所述晶体管 对产生的电流脉冲。

2. 一种使用比特转换点提取电路的时钟恢复电路装置,包括:

预定的第一电流源晶体管;

第一晶体管对,其源极连接在一起,所述源极向所述第一电流源晶体管偏置,并且所述 第一晶体管对通过其栅极被施加有来自外部的差分非归零恢复输入信号;

第一电容器,与所述第一晶体管对和所述第一电流源晶体管连接,以使所述第一电流 源晶体管的输出节点的电压恒定;

预定的第二电流源晶体管;

第二晶体管对,其源极连接在一起,所述第二晶体管对的源极向所述第二电流源晶体 管偏置,并且所述第二晶体管对通过其栅极被施加有来自外部的差分非归零恢复输入信 号;

向所述第二电流源晶体管偏置的所述第二晶体管对,其具有连接至电源电压的一个栅 极端和连接至地电压的另一栅极端;以及第二电容器,连接至所述第二电流源晶体管,以使 所述第二电流源晶体管的输出节点的电压恒定;以及

LC 电压控制振荡器,将所述第一晶体管对和所述第二晶体管对生成的电流脉冲输入到 预定的差分输出端。

3. 一种使用比特转换点提取电路的时钟恢复电路装置,包括:

预定的电流源晶体管;

晶体管对,其源极连接在一起,所述源极向所述电流源晶体管偏置并且所述晶体管对 通过其栅极被施加有来自外部的差分非归零恢复输入信号;

电容器,与所述晶体管对和所述电流源晶体管连接,以使所述电流源晶体管的输出节 点的电压恒定;以及

LC 电压控制振荡器,所述 LC 电压控制振荡器在所述晶体管对的输出端处接收由所述 晶体管对产生的电流脉冲。

4. 一种使用比特转换点提取电路的时钟恢复电路装置,包括:

预定的电流源晶体管;

晶体管对,其源极连接在一起,所述源极向所述电流源晶体管偏置,并且所述晶体管对 通过其栅极被施加有来自外部的差分非归零恢复输入信号;

电容器,与所述晶体管对和所述电流源晶体管连接,以使所述电流源晶体管的输出节 点的电压恒定;以及

LC 电压控制振荡器,通过使用耦合电感器按照在所述电感器中产生的感应电流的形式 接收由所述晶体管对产生的电流脉冲。

5. 根据权利要求1至4中任一项所述的使用比特转换点提取电路的时钟恢复电路装置,

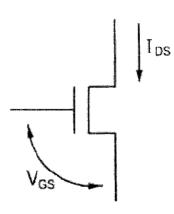

其中,所述电容器使所述晶体管对的 VGS 和 IDS 曲线具有非线性区范围中工作的能力。

6. 根据权利要求 1 至 4 中任一项所述的使用比特转换点提取电路的时钟恢复电路装置,

其中,所述 LC 电压控制振荡器包括可变电容器,所述可变电容器控制预定的振荡信号的频率。

7. 根据权利要求 1 至 4 中任一项所述的使用比特转换点提取电路的时钟恢复电路装置,

其中,所述差分非归零恢复输入信号表示施加至所述晶体管对的第一晶体管的预定值 的正电压以及施加至所述晶体管对的第二晶体管的预定值的负电压。

8. 根据权利要求1至4中任一项所述的使用比特转换点提取电路的时钟恢复电路装置,

其中,所述晶体管对包括 NMOS 晶体管。

9. 根据权利要求1至4中任一项所述的使用比特转换点提取电路的时钟恢复电路装置,

其中,所述比特转换点提取电路是在需要对从所述输入信号中产生的时钟进行同步的 点处产生脉冲信号的电路。

10. 一种控制使用比特转换点提取电路的时钟恢复电路装置的方法,包括以下步骤:

通过具有与预定的电流源晶体管连接的源极端的预定晶体管对从外部接收差分非归 零恢复输入信号;

保持用于将所述电流源晶体管与所述晶体管对连接的节点的电压;以及

通过所述节点的恒定电压和预定的栅极电压来输出预定的偏置电流;

LC 电压控制振荡器向预定的差分输出端输入由所述晶体管对产生的电流脉冲。

11. 根据权利要求 10 所述的控制使用比特转换点提取电路的时钟恢复电路装置的方法,

其中,所述差分非归零恢复输入信号表示施加至所述晶体管对的第一晶体管的预定值的正电压以及施加至所述晶体管对的第二晶体管的预定值的负电压。

12. 根据权利要求 10 所述的控制使用比特转换点提取电路的时钟恢复电路装置的方法,

其中,所述晶体管对包括 NMOS 晶体管。

13. 根据权利要求 10 所述的控制使用比特转换点提取电路的时钟恢复电路装置的方法,

其中,所述比特转换点提取电路装置是在需要对从所述输入信号中产生的时钟进行同步的点处产生脉冲信号的电路。

14. 根据权利要求 10 所述的控制使用比特转换点提取电路的时钟恢复电路装置的方法,

其中,在所述的保持用于将所述电流源晶体管与所述晶体管对连接的节点的电压的步骤中,电容器使所述晶体管对的 VGS 和 IDS 曲线具有非线性区范围中工作的能力。

# 非归零恢复信号的比特转换点提取电路和锁相时钟恢复电 路以及用于控制所述电路的方法

#### 技术领域

[0001] 本发明涉及一种非归零恢复(NRZ-recovery)信号的比特转换点提取电路 (bit-transition point extraction circuit)、一种使用该电路的锁相时钟恢复电路、以 及一种用于控制该电路的方法,且更具体地,涉及一种用于通过提供简单结构的比特转换 点提取装置从非归零恢复输入信号中提取比特转换点的电路(所述电路能够以较高速度 运行)、一种使用该电路的锁相时钟恢复电路、以及一种用于控制该电路的方法。

#### 背景技术

[0002] 输入被调制为非归零恢复码的信号的串行链路接收机等诸如此类的装置在调制 之前基于所产生的时钟产生与输入信号同步的时钟并恢复比特串(bit string)。起上述作 用的装置被称作时钟恢复电路。

[0003] 作为典型的时钟恢复电路,使用锁相环的时钟恢复电路、过采样时钟恢复电路、使用注入锁定 (injection locked) 的振荡器的时钟恢复电路 (此后,称作"注入锁定时钟恢 复电路")等均在使用。

[0004] 在上面所描述的时钟恢复电路中,注入锁定时钟恢复电路通常包括比特转换点提 取电路以及注入锁定振荡器。

[0005] 己知的比特转换提取电路由延迟电路和异或电路构成。输入信号是调制为非归零恢复码的信号。该信号与通过延迟电路的信号一起用做异或电路的输入。

[0006] 此时,如果两个输入彼此不同,则输出1,而如果两个输入彼此相同,则输出0。因此,在输入信号的比特被转换的位置处输出具有信号在延迟电路中被延迟的时间宽度的脉冲。

[0007] 比特转换点提取电路的延迟电路通常被设计为具有一定的延迟值,该延迟值约等 于一比特时间宽度的一半。为此,通过使用延迟电路中的正反馈而配置的环形振荡器而产 生时钟以及通过使用与用于比特转换点提取电路中的环形振荡器相同的延迟电路来必要 地获取延迟值的方法被广泛使用。

[0008] 然而,由于该环形振荡器不适合于快速运行,能够产生比环形振荡器更高频时钟的LC电压控制振荡器普遍用于快速运行的注入锁定时钟恢复电路。在这种情况下,由于需要对延迟电路(其用于比特转换点提取电路以获取一个比特时间宽度的一半)的延迟值进行控制,而异或电路应当能够输出具有较短时间宽度的脉冲,故已知的比特转换点提取电路成为了阻止在高速注入锁定时钟恢复电路中高速运行的瓶颈。

#### 发明内容

[0009] 技术问题

[0010] 设计本发明以解决在相关领域中的上述问题。本发明的一个目的是提供一种具有快速运行结构的 CMOS 比特转换点提取电路。

[0011] 本发明的另一目的是提供一种具有简单结构的比特点提取电路。

[0012] 本发明的又一目的是提供一种注入锁定时钟恢复电路,其能够通过提供具有高速运行的结构的比特转换点提取电路来恢复处于高速的精确时钟。

[0013] 技术方案

[0014] 为了实现上述目的并解决相关领域中的上述问题,根据本发明的示例性实施例的 比特转换点提取电路装置包括:预定的电流源晶体管;以及与源连接的晶体管对,其对电 流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号。

[0015] 根据本发明的另一示意性实施例的比特转换点提取电路装置包括:预定电流源晶体管;与源连接的晶体管对,其对电流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号;以及与晶体管对和电流源晶体管连接的电容器,使得电流源晶体管的输出节点的电压恒定。

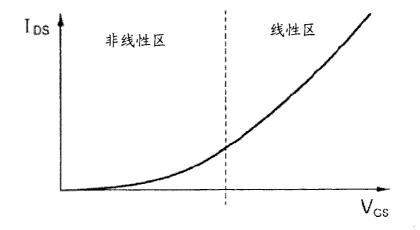

[0016] 此时,电容器允许晶体管对的 V<sub>cs</sub>和 I<sub>Ds</sub> 曲线具有在非线性区域中工作范围的电容。 [0017] 使用根据本发明的示例性实施例的比特转换点提取电路的时钟恢复装置包括:预 定电流源晶体管;与源连接的晶体管对,其对电流源晶体管偏置并施加有来自外部的差分 非归零恢复输入信号;与晶体管对和电流源晶体管连接的电容器,使得电流源晶体管的输 出节点的电压恒定;以及 LC 电压控制振荡器,用于将由晶体管对产生的电流脉冲输出至预 定差分输出端。

[0018] 使用根据本发明的第二示例性实施例的比特转换点提取电路的时钟恢复电路装置包括:预定第一电流源晶体管;与源连接的第一晶体管对,其对第一电流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号;与第一晶体管对和第一电流源晶体管连接的第一电容器,使得第一电流源晶体管的输出节点的电压恒定;预定第二电流源晶体管; 对第二电流源晶体管偏置并具有连接至电源电压的一个栅极以及连接至地电压的另一栅极端的第二晶体管对,并且与第二晶体管对连接的第二电容器,使得第二电流源晶体管的输出节点的电压;以及LC电压控制振荡器,其接收按照差分信号形式轭第二晶体管对的输出。

[0019] 使用根据本发明的另一示例性实施例的比特转换点提取电路的时钟恢复电路装置包括:预定电流源晶体管;与源连接的晶体管对,其对电流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号;与晶体管对和电流源晶体管连接的电容器,使得电流源晶体管的输出节点的电压恒定;以及LC电压控制振荡器,用于接收按照通过使用耦合电感在电感中产生的感应电流的形式由晶体管对产生的电流脉冲。

[0020] 此时, LC 电压控制振荡器包括可变电容器, 用于控制预定振荡信号的频率。

[0021] 根据本发明的示例性实施例的控制比特转换点提取电路的方法包括以下步骤:通 过具有与预定电流源晶体管连接的源极端的预定晶体管对接收来自外部的差分非归零恢 复输入信号;保持连接电流源晶体管和晶体管对的节点的电压;以及输出节点的恒定电压 和预定栅电压的预定偏置电流。

[0022] 有益效果

[0023] 根据本发明,可能提供具有高速工作的结构的 CMOS 比特转换点提取电路。

[0024] 根据本发明,可能提供一种具有简单结构的比特转换点提取电路。

[0025] 根据本发明,可能提供一种注入锁定时钟恢复电路,其通过提供具有高速工作的

结构的比特转换点提取电路能够处于高速的精确时钟。

#### 附图说明

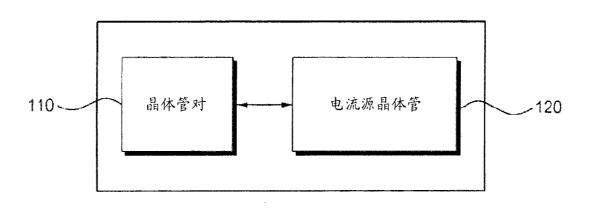

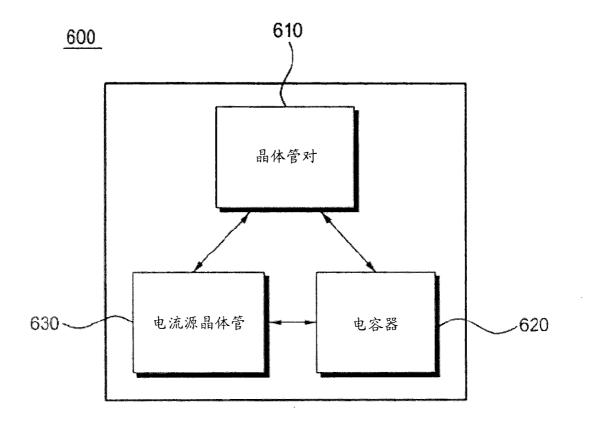

[0026] 图1是示出了根据本发明的示例性实施例的比特转换点提取电路装置的配置的 框图。

[0027] 图 2 是根据本发明的示例性实施例的比特转换点提取电路装置的框图。

[0028] 图 3 是示出了根据本发明的示例性实施例的比特转换点提取电路装置的晶体管的电压 - 电流特性曲线的示图。

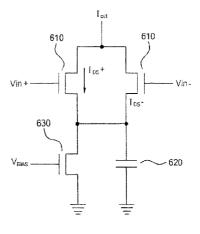

[0029] 图 4 是示出了根据本发明的示例性实施例的比特转换点提取电路的配置的框图。

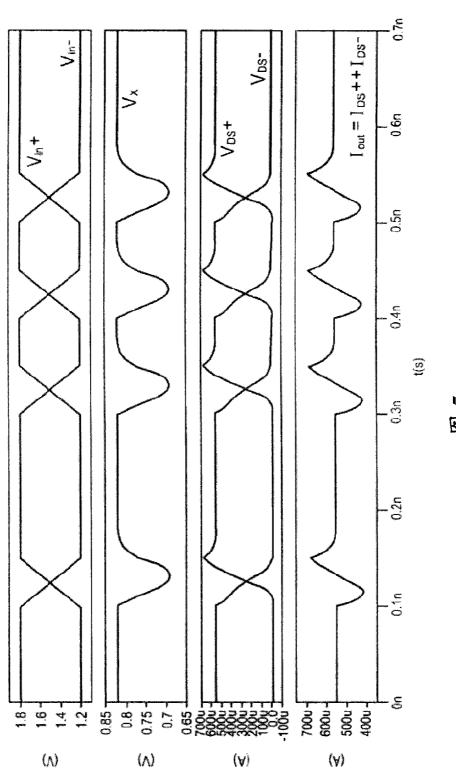

**[0030]** 图 5 是示出了根据本发明的示例性实施例的比特转换点提取电路的预定数据值的曲线图。

[0031] 图 6 是示出了根据本发明的另一实施例的比特转换点提取电路装置的配置的框图。

[0032] 图 7 是示出了根据本发明的另一示例性实施例的比特转换点提取电路的配置的 框图。

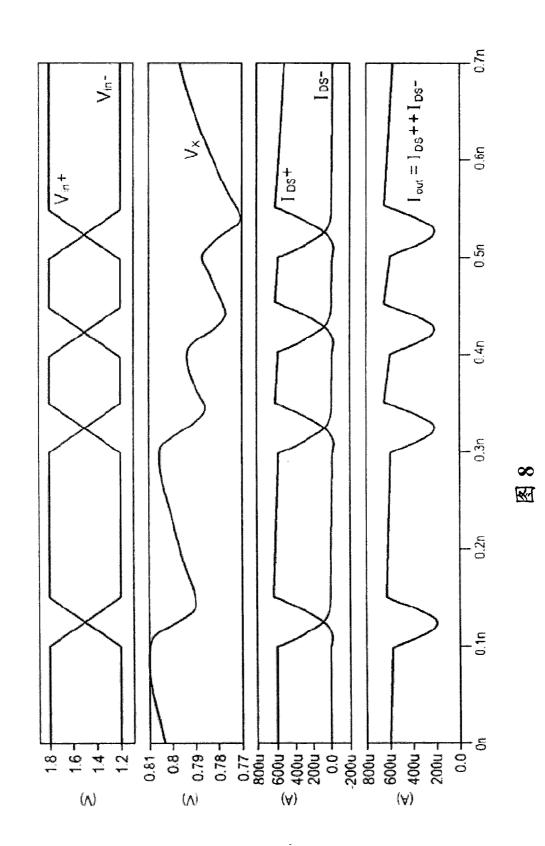

[0033] 图 8 是示出了根据本发明的另一示例性实施例的比特转换点提取电路的预定数据值的曲线图。

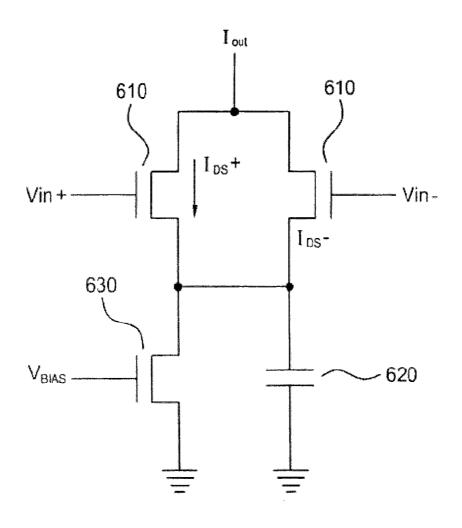

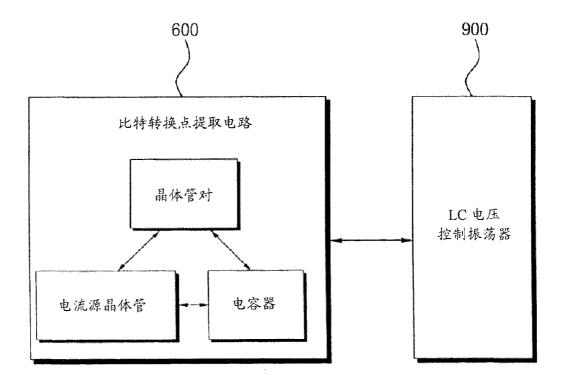

[0034] 图 9 是示出了使用根据本发明的示例性实施例的比特转换点提取电路的时钟恢 复电路装置的配置的框图。

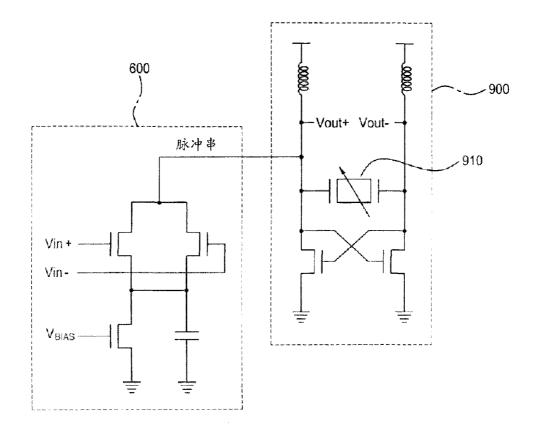

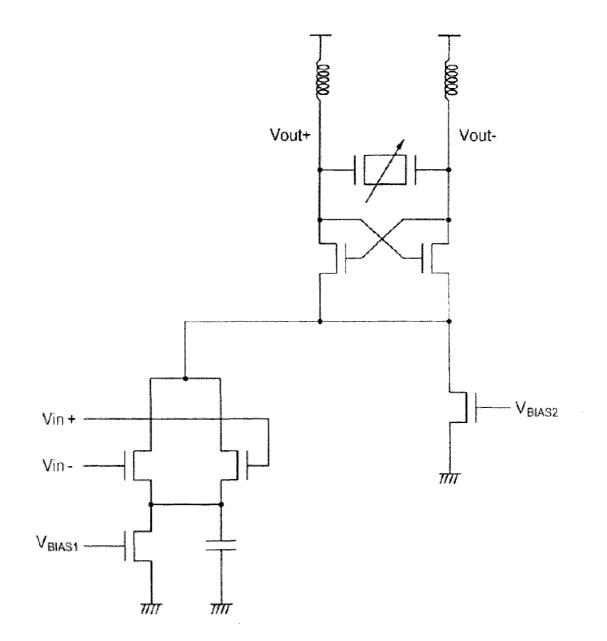

[0035] 图 10 是示出了使用根据本发明的示例性实施例的比特转换点提取电路的时钟恢 复电路的配置的示图。

[0036] 图 11 是示出了根据本发明的示例性实施例的时钟恢复电路的预定数据值的曲线 图。

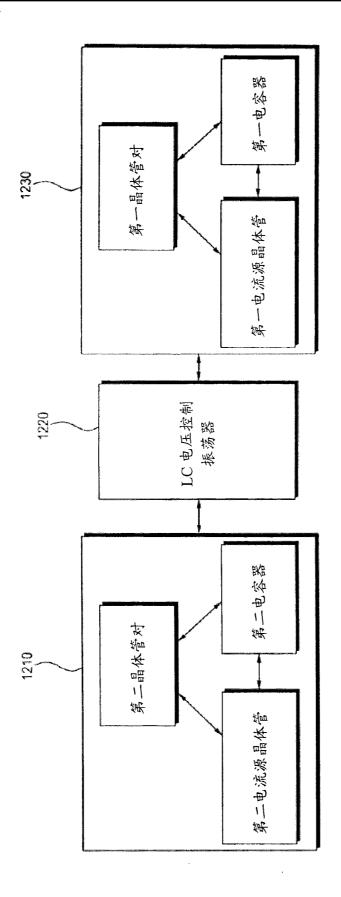

[0037] 图 12 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路装置的配置的框图。

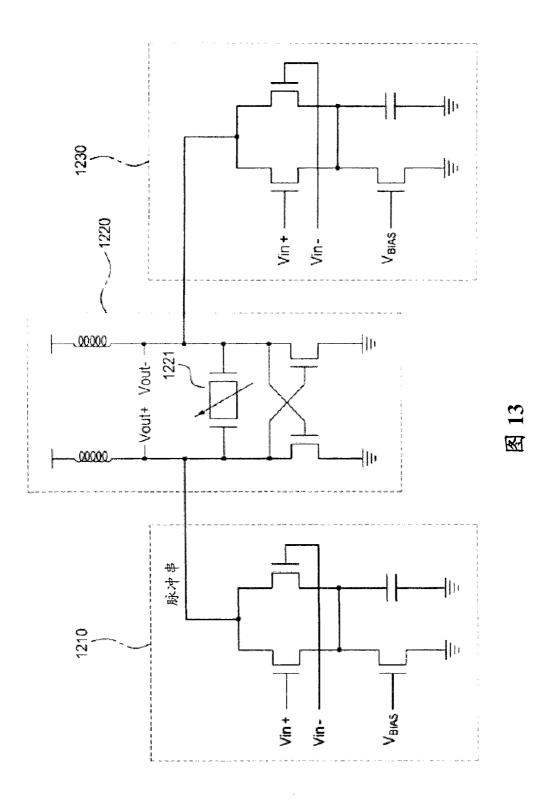

[0038] 图 13 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路的配置的示图。

[0039] 图 14 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路装置的配置的电路图。

[0040] 图 15 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路装置的配置的电路图。

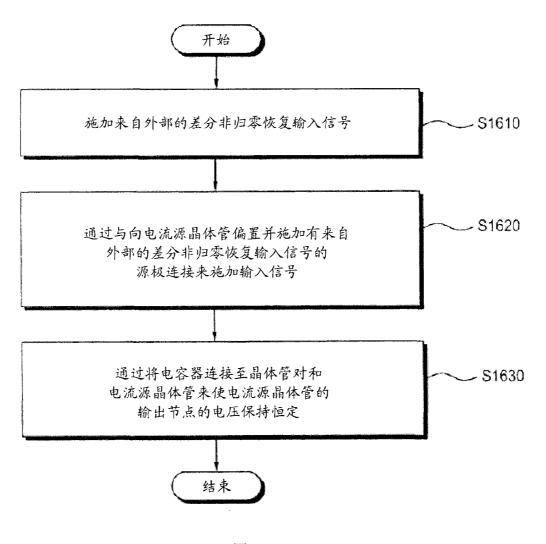

[0041] 图 16 是示出了用于控制根据本发明的示例性实施例的比特转换点提取电路装置的方法的流程图。

#### 具体实施方式

[0042] 此后,尽管下文中将参考附图和在附图中所描述的内容来详细描述本发明的优选 实施例,但本发明并不限于或限定于该优选实施例。

[0043] 图1是示出了根据本发明的示例性实施例的比特转换点提取电路装置的配置的 框图。图2是根据本发明的示例性实施例的比特转换点提取电路装置的晶体管的框图。图

3 是示出了根据本发明的示例性实施例的比特转换点提取电路装置的晶体管的电压 - 电流特性曲线的示图。

[0044] 本发明基于比特转换点提取电路装置,其能够通过使用晶体管接收从外部所施加的差分非归零恢复(NRZ-recovery)输入信号来提取用以恢复初始时钟信号的比特转换点。

[0045] 如图 2 和 3 所示,本发明的比特转换点提取电路装置使用通用 NMOS 晶体管的驱动 原理。如图 3 的曲线中所示, NMOS 晶体管使与 VGS 的平方成比例的 IDS 流动。

[0046] 基于晶体管的上述特性,根据这些部件的工作顺序来顺序地描述比特转换点提取 电路装置 100 的各部分。

[0047] 首先,施加向电流源晶体管 120 偏置的差分非归零恢复输入信号。

[0048] 接下来,一对晶体管110与源极连接,该源极向电流源晶体管120偏置并施加有来 自外部的差分非归零恢复输入信号,以使与电流源晶体管120连接的节点的电压根据从外 部施加的差分非归零恢复输入信号来变化。

[0049] 此时,差分非归零恢复输入信号表示一对电压,包括:在两个预定电压值1和0之间移动的电压的、施加至晶体管对110中的第一晶体管的电压;以及在与施加至第一晶体管的电压的相对方向上移动同时在这两个电压之间移动的、施加至晶体管对中的第二晶体管的电压。

[0050] 如上所述,在本发明中,主要使用 NMOS 晶体管作为晶体管对 110,但并不限于 NMOS 晶体管。

[0051] 图 4 是示出了根据本发明的示例性实施例的比特转换点提取电路的配置的框图。 图 5 是示出了根据本发明的示例性实施例的比特转换点提取电路的预定数据值的曲线图。

[0052] 即,作为晶体管对 110 的 NMOS 晶体管的漏电流 IDS+和 IDS-根据差分非归零恢复 输入信号 Vin+和 Vin-(其将 0 转换至 1 或将 1 转换至 0)来改变。理想地,两个漏电流的 和应当是恒定的。然而,NMOS 晶体管执行与源极跟随器相同的操作,因而 VX 节点的电压根据 Vin+和 Vin-之间的较高电压来变化,以根据电流源晶体管 120 的有限输出阻抗来调制 偏置电流 IBIAS。

[0053] 此时,比特转换点提取电路装置 100 是在需要对从输入信号产生的时钟进行同步的点处产生脉冲信号的电路。

[0054] 即,晶体管对100的漏电流的和等于电流源晶体管120的偏置电流IBIAS,因此,比 特转换点提取电路装置100可以通过获得电流的和来检测用作输入的差分非归零恢复信 号由0变为1或由1变为0的点。

[0055] 图 6 是示出了根据本发明的另一实施例的比特转换点提取电路装置的配置的框图。

[0056] 在根据本发明的示例性实施例的比特转换点提取电路装置100(其在图1中示出)中,两个 NMOS 晶体管以与源极跟随器相同的方式工作,使 VX 节点的移动电压调制该电流,但在这种情况下,两个 NMOS 晶体管在图 3 曲线的线性区中工作,因此,经调制的电流的总量会很小。

[0057] 因此,在本发明中,可以仅通过使用比特转换点提取电路装置 100 检测比特转换的点,但也可以通过在 VX 节点处添加电容器来使电压平稳,并通过使晶体管对 610 在图 3

的曲线图的非线性区内工作来使经调制的偏置电流量最大化。

[0058] 基于上述描述,将根据用于驱动比特转换点提取电路装置的各部分的方法来顺序 地描述根据本发明的另一实施例的比特转换点提取电路。

[0059] 首先,晶体管对 610 具有源极端,源极端与电流源晶体管 630 公共地连接,并施加 有来自外部的差分非归零恢复输入信号。

[0060] 此时,差分非归零恢复输入信号表示施加至晶体管对 610 中的第一晶体管的预定 值的正电压,以及施加至晶体管对中的第二晶体管的预定值的负电压。

[0061] 如上所述,在本发明中,主要使用 NMOS 晶体管作为晶体管对 610,但并不限于 NMOS 晶体管。

[0062] 图 7 是示出了根据本发明的另一示例性实施例的比特转换点提取电路的配置的 框图。图 8 是示出了根据本发明的另一示例性实施例的比特转换点提取电路的预定数据值 的曲线图。

[0063] 接下来,电容器 620 连接至晶体管对 610 和电流源晶体管 630,以使用于连接电流 源晶体管 630 和晶体管对 610 的节点的电压恒定。

[0064] 此时,电容器 620 主要用于使晶体管对 610 的 VGS 和 IDS 曲线具有非线性区中工 作范围的电容量。

[0065] 接下来,电流源晶体管 620 输出根据节点的恒定电压和预定的输出阻抗来调制的 偏置电流。

[0066] 此时,比特转换点提取电路装置 100 是在需要对从输出信号产生的时钟进行同步的点处产生脉冲信号的电路。

[0067] 因此,本发明可以通过将电容器 620 添加至 VX 节点而非通过使用 VX 节点的电压 来调制电流源晶体管 630 的偏置电流来稳定 VX 节点的电压,因此本发明可以通过使晶体管 对 610 在图 3 的曲线图的非线性区中工作来使偏置电流的经调制的总量最大化。

[0068] 因此,图3的曲线图的经调制的电流量与图8的曲线图的电流量相差约两倍或更多。

[0069] 即,本发明电路中的输入信号的比特转换可以产生电流脉冲。最后,所产生的电流脉冲的宽度等于输入信号的转换时间。

[0070] 在电路以高速运行的情况下,比特转换时间通常占用对应于一个或更多比特的时间的一半。由于此特性,可以不附加延迟元件而将电路配置为适于注入锁定(injection locking)。

[0071] 图 9 是示出了使用根据本发明示例性实施例的比特转换点提取电路的时钟恢复 电路装置的配置的框图。

[0072] 可以将上述比特转换点提取电路 600 以及 LC 电压控制振荡器连接来配置本发明的时钟恢复电路。

[0073] 图 10 是示出了使用根据本发明示例性实施例的比特转换点提取电路的时钟恢复 电路的配置的示图。

[0074] 本发明基于比特转换点提取电路装置,所述电路装置能够使用晶体管通过接收来自外部的差分非归零恢复输入信号,来提取提供用于恢复初始时钟的信号的比特转换点。

[0075] 随后将参考比特转换点提取电路装置 600 和 LC 电压控制振荡器 900 的部件之间

的关系来描述时钟恢复电路。

[0076] 可以通过使用比特转换点提取电路装置 600 驱动本发明的时钟恢复电路。下面将 简要描述比特转换点提取电路装置 600 的详细配置。

[0077] 根据本发明的示例性实施例的比特转换点提取电路装置 600 包括:电流源晶体管 630、与源极连接的晶体管对 610(所述源极向电流源晶体管 630 偏置且施加有来自外部的 差分非归零恢复输入信号)、以及与晶体管对 610 和电流源晶体管 620 连接的电容器,使得 电流源晶体管 630 的输出节点的电压恒定。

[0078] 通过与LC电压控制振荡器 900 连接来配置本发明的时钟恢复电路装置,所述LC电压控制振荡器输入电流脉冲,其中,由转换点提取电路装置 600 和晶体管对 610 将一比特转换至预定的差分输出端。

[0079] 这里, LC 电压控制振荡器 900 包括可变电容器 910, 其控制振荡信号的频率。

[0080] 即,LC电压控制振荡器 900 可以通过控制可变电容器 910 来控制振荡信号的频率。 当振荡器 900 通过控制可变电容器 910 对具有频率接近于输入信号的比特率的时钟进行振 荡时,LC电压控制振荡器 900 产生与输入信号同步的时钟,并与此同时在电流脉冲中被注 入锁定。

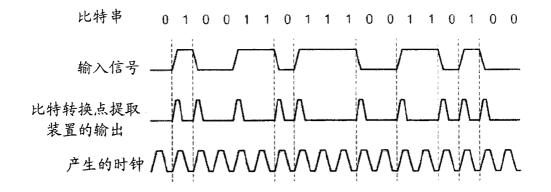

[0081] 图 11 是示出了根据本发明的示例性实施例的时钟恢复电路的预定数据值的曲线 图。

[0082] 可以通过经注入锁定的时钟恢复电路来说明这种原理。本发明的时钟恢复电路还 通过使用用于分别将 0 和 1 对应于低电压和高电压的非归零恢复码来调制和传输 0 和 1。 该信号用作时钟恢复电路的输入信号。

[0083] 如图 11 所示,比特转换点提取电路 600 在从被同步的输入信号中产生时钟的点(即,比特将 0 变换至 1 或将 1 变换至 0 的点)处产生脉冲。

[0084] 此时,LC电压控制振荡器 900(其为经注入锁定的振荡器)是产生时钟的振荡器。 LC电压控制振荡器 900具有通过接收具有频率接近于所产生的时钟频率的信号而使所产 生的时钟与输入信号同步的功能。

[0085] 在使用经注入锁定的振荡器的时钟恢复电路中,从比特转换提取电路所提取的脉冲列(train)被输入至经注入锁定的振荡器,所述振荡器以接近于输入信号的比特率的频率进行振荡,因而,产生了与输入信号的比特串同步的时钟。

[0086] 即,在施加除非归零输入信号之外的用于周期性产生时钟的输入信号的情况下, 使用经注入锁定的振荡器的时钟恢复电路可以用于频率乘法器。

[0087] 在本发明中,比特转换点提取电路装置 600 可以仅连接至 LC 电压控制振荡器 900 的差分输出的一侧,而比特转换点提取电路装置 600 连接至 LC 电压控制振荡器 900 的差分输出的两侧中的每一侧。在这种情况下,两侧中的任意一侧用作比特转换点提取电路装置 而另一侧用作偏置电路,因此可以配置出更为稳定的时钟恢复电路。

[0088] 图 12 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路装置的配置的框图。

[0089] 如图中所示,现在将描述使用根据本发明的另一示例性实施例的比特转换点提取 电路的时钟恢复电路的配置。

[0090] 时钟恢复电路包括第一比特转换点提取电路装置 1210, 其包括: 预定的第一电流

源晶体管;与源极连接的晶体管对,所述源极向第一电流源晶体管偏置并施加有来自外部的差分非归零恢复输入信号;以及第一电容器,与第一晶体管对和第一电流源晶体管连接,以使第一电流源晶体管的输出节点的电压恒定。时钟恢复电路还包括第二比特转换点提取电路装置1230,其包括:预定的第二电流源晶体管;第二晶体管对,向第二电流源晶体管偏置,并具有连接至电源电压的一个栅极端和连接至地电压的另一栅极端;以及第二电容器,连接至第二电流源晶体管,以使第二电流源晶体管的输出节点的电压恒定。时钟恢复电路还包括LC电压控制振荡器1220,按照差分信号的形式接收第二晶体管对的输出。

[0091] 时钟恢复电路装置还包括比特转换点提取电路 600 和 LC 电压控制振荡器 1220。因此,将省略各构成元件的详细描述。

[0092] 图 13 是示出了使用根据本发明的另一实施例的比特转换点提取电路的时钟恢复 电路的配置的示图。

[0093] 即,如图 13 所示,第一比特转换点提取电路装置 1210 在通过输入差分非归零恢复 信号来转换比特的点处产生电流脉冲,以将电流脉冲输入至 LC 电压控制振荡器 1220 的任 一差分输出,而第二比特转换点提取电路 1230 连接至 LC 电压控制振荡器 1220 的另一差分 输出,以用作恒定电流偏置电路。

[0094] 此时,LC电压控制振荡器 1220 可以通过控制电容器 1221 来控制信号振荡的频率。 当 LC 电压控制振荡器 1220 对频率接近于输入信号的比特率的时钟进行振荡时,LC 电压控 制振荡器 1220 可以通过在电流脉冲中注入锁定而产生与输入信号同步的时钟。

[0095] 图 14 是示出了使用根据本发明的另一实施例的比特转换点提取电路的时钟恢复 电路装置的配置的电路图。

[0096] 如图中所示,使用本发明的比特转换点提取电路的时钟恢复电路装置 1400 可以 配置为由 LC 电压控制振荡器的一侧处的偏置电压恒定保持的时钟恢复电路。现在将描述 这种配置。

[0097] 使用比特转换点提取电路的时钟恢复电路装置 1400 包括:预定的电流源晶体管; 晶体管对,与源极连接,所述源极向电流源晶体管偏置并施加有来自外部的差分非归零恢 复输入信号;电容器,将晶体管对与电流源晶体管相连,以使电流源晶体管输出节点的电压 恒定;以及LC电压控制振荡器,所述LC电压控制振荡器在电流源晶体管的输出端处接收由 晶体管对产生的电流脉冲。

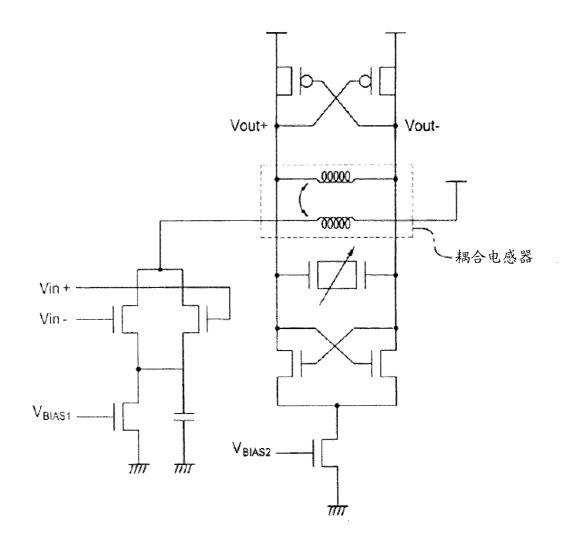

[0098] 图 15 是示出了使用根据本发明的另一示例性实施例的比特转换点提取电路的时 钟恢复电路装置的配置的电路图。

[0099] 如图 15 中所示,可以通过将耦合电感器 (coupled inductor) 添加至 LC 电压控制 振荡器来配置使用本发明的比特转换点提取电路的时钟恢复电路装置 1400。现在将描述这 种配置。

[0100] 使用比特转换点提取电路的时钟恢复电路装置 1500 包括:预定的电流源晶体管; 晶体管对,与源极连接,所述源极向电流源晶体管偏置并施加有来自外部的差分非归零恢 复输入信号;电容器,将晶体管对与电流源晶体管相连,以使电流源晶体管输出节点的电压 恒定;以及 LC 电压控制振荡器,通过使用耦合电感器按照在电感器中所产生的感应电流的 形式来接收由晶体管对产生的电流脉冲。

[0101] 图 16 是示出了用于控制根据本发明的示例性实施例的比特转换点提取电路装置

的方法的流程图。

[0102] 可以通过使用比特转换点提取电路装置 600 来执行用于控制本发明的比特转换 点提取电路装置的方法。根据比特转换点提取电路装置 600 的驱动方法来进行顺序地描述。

[0103] 首先,电流源晶体管 630 接收来自外部的差分非归零恢复输入信号(S1610)。

[0104] 接下来,将晶体管对 610 与源极连接,所述源极向电流源晶体管 630 偏置并施加有来自外部的差分非归零恢复输入信号,从而所述晶体管对施加有该输入信号(S1620)。

[0105] 此时,差分非归零恢复输入信号表示施加至晶体管对 610 的第一晶体管的预定值的正电压,以及施加至晶体管对的第二晶体管的预定值的负电压。

[0106] 如上所述,在本发明中,主要使用 NMOS 晶体管作为晶体管对 610,但并不限于 NMOS 晶体管。

[0107] 接下来,电容器 620 连接至晶体管对 610 和电流源晶体管 630,使得电流源晶体管 630 的输出节点的电压恒定 (S1630)。

**[0108]** 电容器 620 使晶体管对 610 的 VGS 和 IDS 曲线的工作范围能够 (have a capacity of) 处于非线性区。

[0109] 此时,比特转换点提取电路装置 600 可以表示用于对在从输入信号产生的时钟进行同步的点处产生脉冲信号的电路。

[0110] 按照程序命令(其可以通过多种计算机组件执行并可以被记录在计算机可读介质中)的形式实施本发明的示例性实施例。计算机可读介质可以包括独立形式或组合形式的程序命令、数据文件数据结构等。记录在介质中的程序命令被具体设计或配置用于本发明,但可以作为计算机软件领域的普通技术人员的公知技术来使用。计算机可读记录介质包括例如存储和执行程序命令的磁介质(诸如硬盘、软盘、以及磁带)、光学记录介质(诸如 CD-ROM 和 DVD)、磁光(magneto-optical)介质(诸如可光读磁盘)、以及硬件装置(诸如 ROM、RAM、闪存)等。程序命令处理包括例如由编译器预备的机器语言之外通过使用解释程序由计算机执行的高级语言码。为了执行本发明的操作,可以通过一个或多个软件对硬件装置进行操作。反之亦然。

[0111] 如上所述,尽管已参考有限的实施例和附图描述了本发明,但本发明并不限于这些实施例并且可以由本领域的技术人员做出多种变换和修改。因此,本发明的范围不应当限于上述实施例而应当由所附权利要求及其等同替代物来定义。

[0112] 标号列表

[0113] 600:比特转换点提取电路

[0114] 610:晶体管对

- [0115] 620:电容器

- [0116] 630:电流源晶体管

- [0117] 900:LC 电压控制振荡器

.

100

图 2

图 3

图 4

说明书附

冬

图 2

图 7

17

-

图 9

图 10

图 11

,

\_

-

图 14

图 15

图 16