# 2013 International SoC Design Conference

**Conference Information**

**Papers**

**Sponsors**

http://www.isocc.org

Copyright and Reprint Permission: Abstracting is permitted with credit to the source. Libraries are permitted to photocopy beyond the limit of U.S. copyright law for private use of patrons those articles inthis volume that carry a code at the bottom of the first page, provided the per-copy fee indicated in the code is paid through Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923. Forother copying, reprint or republication permission, write to IEEE Copyrights Manager, IEEE Operations Center, 445 Hoes Lane, Piscataway, NJ 08854. All rights reserved. Copyright ©2013 by IEEE.

IEEE Catalog Number : CFP1369E-USB ISBN : 978-1-4799-1141-7

## 2013 International SoC Design Conference

| CDC(P)-162 | Electromagnetic Immunity Enhancement using Active Decoupling Capacitor  JiSoo Hwang, NaHyun Kim, JeongMin Jo and SoYoung Kim  Sungkyunkwan University, Korea 162                                 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDC(P)-163 | Design of Hybrid Bias Modulator for Envelope Tracking Technique Hearyun Jung, Junghyun Ham, Hyungchul Kim, Wonseob Lim, Minchul Kang and Youngoo Yang Sungkyunkwan University, Korea 163         |

| CDC(P)-164 | Design of Differential Common-Source CMOS Power Amplifier Junghyun Ham, Hyungchul Kim, Hearyun Jung, Wonseob Lim and Youngoo Yang Sungkyunkwan University, Korea 164                             |

| CDC(P)-165 | Efficiency Enhanced CMOS Power Amplifier Using Dynamic Bias Switching Circuit  Hyungchul Kim, Junghyun Ham, Jehyeon Gu and Yougoo Yang  Sungkyunkwan University, Korea 165                       |

| CDC(P)-166 | High Efficiency Transmitter and Receiver for Magnetic Resonant Wireless Power Transfer System  Jae-Hyeong Jang, Hyung-Gu Park, Ji-Hun Kang and Kang-Yoon Lee  SungKyunKwan University, Korea 166 |

| CDC(P)-167 | A 15b Second-Order Integrating ∑ △ A/D Converter  Joongho Choi  University of Seoul, Korea 167                                                                                                   |

| CDC(P)-168 | Design of PFM Boost Converter Kichang Jang, Chulkyu Park, Jihwan Kim, Ikhyun Kim, Joonho Park and Joongho Choi University of Seoul, Korea  168                                                   |

| CDC(P)-169 | All-digital Process-Variation-Calibrated Timing Generator for ATE  Kyungho Ryu, Dong-Hoon Jung and Seong-Ook Jung  Yonsei University, Korea  169                                                 |

| CDC(P)-170 | A 5-Gb/s Adaptive Equalizer & Duty-Cycle Corrector Using Asynchronous Under-Sampling Histogram Wang-Soo Kim and Woo-Young Choi Yonsei University, Korea 170                                      |

| CDC(P)-171 | A 0.4-V 88-uW 200-MHz PLL with reduced reference spurs.  Joung-Wook Moon, Kwang-Chun Choi and Woo-Young Choi  Yonsei University, Korea 171                                                       |

## **CDC Demo Session**

09:00~17:00 Lobby

Chair: Kwang Hyun Baek (Chung-Ang University, Korea) Kyoung Rok Cho (Chungbuk National University, Korea)

# A 0.4-V 88-μW 200-MHz PLL with Reduced Reference Spurs.

Joung-Wook Moon, Kwang-Chun Choi, and Woo-Young Choi Department of Electrical and Electronic Engineering, Yonsei University Seodaemun-gu, Seoul 120-749, Korea wchoi@yonsei.ac.kr

#### I. INTRODUCTION

There are increasing demands for ICs with reduced power consumption as well as enhanced power efficiency. One method of reducing power consumption is lowering supply voltages. For this reason, there have been many attempts to realize PLLs with Ultra-Low Voltage (ULV) supplies [1]. However, reducing supply voltages less than 0.5 V is not easy due to the multi-stacked charge pump and voltage headroom. We present a 200 MHz PLL operating at 0.4 V with reduced reference spurs.

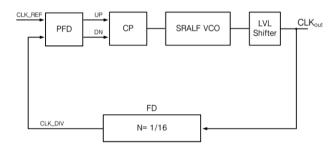

Fig. 1. Proposed PLL architecture

#### II. DESCRIPTION

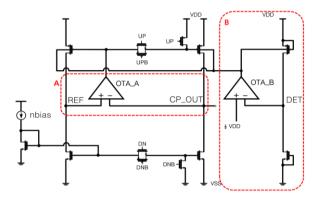

Fig. 1 shows overall PLL architecture. It consists of a conventional DFF-based phase-frequency detector (PFD), a low-voltage charge pump (CP) and a supply-regulated active-loop filter VCO (SRALF VCO) [2]. The 1/16 frequency division (FD) is realized with an ETSPC and 3 stages of TSPC dividers. Fig. 2 shows the proposed CP circuit. In Block A, with OTA\_A,  $V_{\rm REF}$  at REF node follows  $V_{\rm CP_OUT}$  at CP\_OUT node. In Block B, a feedback loop detects the off-path voltage  $V_{\rm DET}$  at DET node and compensates the body-bias voltage of PMOS transistors. In this way, CP circuit compensates charging/ discharging current and leakage current mismatches, which induce PLL reference spurs.

#### III. CHIP IMPLEMENTAION AND MEASUREMENT RESULTS

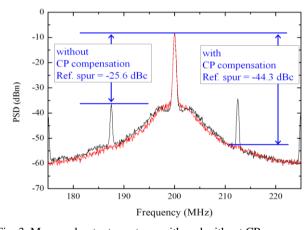

Fig. 3 shows the measured PLL output spectra with and without CP compensation. The center frequency is 200 MHz with 50 MHz span. The reference spur is reduced from -25.67 dBc to -44.3 dBc. This clearly shows that our CP mismatch and leakage current compensation technique successfully work.

Fig. 2. Proposed charge pump circuit

Fig. 3. Measured output spectrum with and without CP compensation

The prototype ULV PLL is fabricated with 130-nm CMOS technology. It consumes only 88  $\mu W$  and achieves 0.44-mW/GHz of record-low power efficiency among ULV PLLs reported so far.

#### REFERENCE

- [1] Wu-Hsin Chen, Wing-Fai Loke, and Byunghoo Jung, "A 0.5-V, 440-uW frequency synthesizer for implantable medical devices," *IEEE Journal of Solid-State Circuits*, vol. 47, no. 8, pp.1896-1907, August 2012

- [2] Kwang-Chun Choi, Sung-Guen Kim, Seung-Woo Lee, Bhum-Cheol Lee, and Woo-Young Choi, "A 990-uW 1.6-GHz PLL based on a novel supply-regulated active-loop-filter vco" *IEEE Trans. on Circuits and Systems II: Express Briefs*, vol.60, no.6, pp. 311-315, June 2013.

This work [2012R1A2A1A01009233] was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MEST). The authors are very thankful to IC Design Education Center (IDEC) for EDA software support as well as chip fabrication.